# UC3842/UC3843/UC3844/UC3845 **SMPS** Controller

# **Features**

- Low Start up Current

- Maximum Duty Clamp

- UVLO With Hysteresis

- · Operating Frequency up to 500KHz

# Description

The UC3842/UC3843/UC3844/UC3845 are fixed frequencycurrent-mode PWM controller. They are specially designed for Off-Line and DC to DC converter applications with minimum external components. These integrated circuits feature a trimmed oscillator for precise duty cycle control, a temperature compensated reference, high gain error amplifier, current sensing comparator and a high current totempole output for driving a Power MOSFET. The UC3842 and UC3844 have UVLO thresholds of 16V (on) and 10V (off). The UC3843 and UC3845 are 8.5V(on) and 7.9V (off). The UC3842 and UC3843 can operate within 100% duty cycle. The UC3844 and UC3845 can operate with 50% duty cycle.

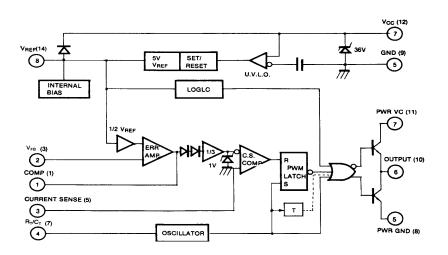

# **Internal Block Diagram**

\* NORMALLY 8DIP/8SOP PIN NO.

() IS 14SOP PINNO. TOGGLE FLIP FLOP USED ONLY IN UC3844, UC3845

# **Absolute Maximum Ratings**

| Parameter                                        | Symbol                   | Value       | Unit |

|--------------------------------------------------|--------------------------|-------------|------|

| Supply Voltage                                   | Vcc                      | 30          | V    |

| Output Current                                   | lo                       | ±1          | А    |

| Analog Inputs (Pin 2.3)                          | V(ANA)                   | -0.3 to 6.3 | V    |

| Error Amp Output Sink Current                    | ISINK (E.A)              | 10          | mA   |

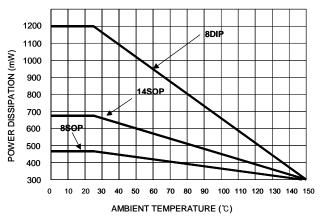

| Power Dissipation at T <sub>A</sub> ≤25°C (8DIP) | P <sub>D</sub> (Note1,2) | 1200        | mW   |

| Power Dissipation at T <sub>A</sub> ≤25°C (8SOP) | P <sub>D</sub> (Note1,2) | 460         | mW   |

| Power Dissipation at TA≤25°C (14SOP)             | PD(Note1,2)              | 680         | mW   |

| Storage Temperature Range                        | TSTG                     | -65 ~ +150  | °C   |

| Lead Temperature (Soldering, 10sec)              | TLEAD                    | +300        | °C   |

#### Note:

1. Board Thickness 1.6mm, Board Dimension 76.2mm ×114.3mm, (Reference EIA / JSED51-3, 51-7)

2. Do not exceeed PD and SOA (Safe Operation Area)

# **Power Dissipation Curve**

# **Thermal Data**

| Characteristic                      | Symbol        | 8-DIP | 8-SOP | 14-SOP | Unit |

|-------------------------------------|---------------|-------|-------|--------|------|

| Thermal Resistance Junction-ambient | Rthj-amb(MAX) | 100   | 265   | 180    | °C/W |

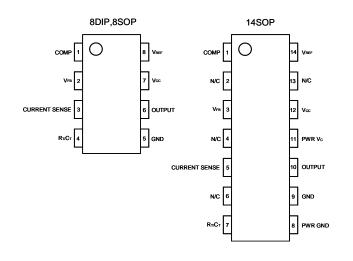

# **Pin Array**

# **Electrical Characteristics**

| Parameter                        | Symbol           | Conditions                                     | Min. | Тур. | Max. | Unit |

|----------------------------------|------------------|------------------------------------------------|------|------|------|------|

| REFERENCE SECTION                |                  |                                                |      |      |      |      |

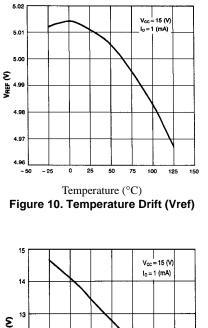

| Reference Output Voltage         | Vref             | $T_J = 25^{\circ}C$ , $I_{REF} = 1mA$          | 4.90 | 5.00 | 5.10 | V    |

| Line Regulation                  | $\Delta V_{REF}$ | $12V \le V_{CC} \le 25V$                       | -    | 6    | 20   | mV   |

| Load Regulation                  | $\Delta VREF$    | $1mA \le IREF \le 20mA$                        | -    | 6    | 25   | mV   |

| Short Circuit Output Current     | Isc              | $T_A = 25^{\circ}C$                            | -    | -100 | -180 | mA   |

| OSCILLATOR SECTION               |                  |                                                |      |      |      |      |

| Oscillation Frequency            | f                | $T_J = 25^{\circ}C$                            | 47   | 52   | 57   | kHz  |

| Frequency Change with<br>Voltage | Δf/ΔVcc          | $12V \le V_{CC} \le 25V$                       | -    | 0.05 | 1    | %    |

| Oscillator Amplitude             | Vosc             | -                                              | -    | 1.6  | -    | VP-P |

| ERROR AMPLIFIER SECTION          | N                |                                                |      |      |      |      |

| Input Bias Current               | IBIAS            | -                                              | -    | -0.1 | -2   | μA   |

| Input Voltage                    | VI(E>A)          | Vpin1 = 2.5V                                   | 2.42 | 2.50 | 2.58 | V    |

| Open Loop Voltage Gain           | Gvo              | $2V \le V_O \le 4V$ (Note3)                    | 65   | 90   | -    | dB   |

| Power Supply Rejection Ratio     | PSRR             | $12V \le V_{CC} \le 25V$ (Note3)               | 60   | 70   | -    | dB   |

| Output Sink Current              | ISINK            | Vpin2 = 2.7V, Vpin1 = 1.1V                     | 2    | 7    | -    | mA   |

| Output Source Current            | ISOURCE          | Vpin2 = 2.3V, Vpin1 = 5V                       | -0.6 | -1.0 | -    | mA   |

| High Output Voltage              | Voh              | $V_{pin2}$ = 2.3V, $R_L$ = 15k $\Omega$ to GND | 5    | 6    | -    | V    |

| Low Output Voltage               | Vol              | $V_{pin2} = 2.7V$ , $R_L = 15k\Omega$ to Pin 8 | -    | 0.8  | 1.1  | V    |

| CURRENT SENSE SECTION            | •                |                                                |      |      |      |      |

| Gain                             | Gv               | (Note 1 & 2)                                   | 2.85 | 3    | 3.15 | V/V  |

| Maximum Input Signal             | VI(MAX)          | Vpin1 = 5V(Note 1)                             | 0.9  | 1    | 1.1  | V    |

| Power Supply Rejection Ratio     | PSRR             | 12V ≤ V <sub>CC</sub> ≤ 25V (Note 1,3)         | -    | 70   | -    | dB   |

| Input Bias Current               | IBIAS            | -                                              | -    | -3   | -10  | μA   |

| OUTPUT SECTION                   |                  |                                                |      |      |      |      |

| Low Output Voltage               | Vol              | ISINK = 20mA                                   | -    | 0.08 | 0.4  | V    |

|                                  |                  | ISINK = 200mA                                  | -    | 1.4  | 2.2  | V    |

| High Output Voltage              | Voн              | ISOURCE = 20mA                                 | 13   | 13.5 | -    | V    |

|                                  |                  | ISOURCE = 200mA                                | 12   | 13.0 | -    | V    |

| Rise Time                        | tR               | TJ = 25°C, CL= 1nF (Note 3)                    | -    | 45   | 150  | ns   |

| Fall Time                        | tF               | TJ = 25°C, CL= 1nF (Note 3)                    | -    | 35   | 150  | ns   |

| UNDER-VOLTAGE LOCKOUT            | SECTION          | ·                                              | •    |      |      | ·    |

| Start Threshold                  | VTH(ST)          | UC3842/UC3844                                  | 14.5 | 16.0 | 17.5 | V    |

|                                  |                  | UC3843/UC3845                                  | 7.8  | 8.4  | 9.0  | V    |

| Min. Operating Voltage           |                  | UC3842/UC3844                                  | 8.5  | 10.0 | 11.5 | V    |

| (After Turn On)                  | VOPR(MIN)        | UC3843/UC3844                                  | 7.0  | 7.6  | 8.2  | V    |

## Electrical Characteristics (Continued)

(VCC=15V, RT=10kΩ, CT=3.3nF, TA= 0°C to +70°C, unless otherwise specified)

| Parameter                | Symbol   | Conditions     | Min. | Тур. | Max. | Unit |

|--------------------------|----------|----------------|------|------|------|------|

| PWM SECTION              |          |                |      |      |      |      |

| May Duty Cycle           | D(Max)   | UC3842/UC3843  | 95   | 97   | 100  | %    |

| Max. Duty Cycle          | D(Max)   | UC3844/UC3845  | 47   | 48   | 50   | %    |

| Min. Duty Cycle          | D(MIN)   | -              | -    | -    | 0    | %    |

| TOTAL STANDBY CURRENT    |          |                |      |      |      |      |

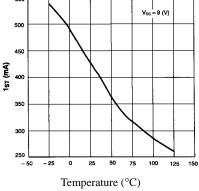

| Start-Up Current         | IST      | -              | -    | 0.45 | 1    | mA   |

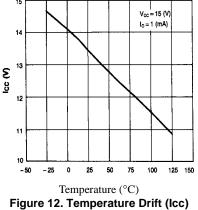

| Operating Supply Current | ICC(OPR) | Vpin3=Vpin2=ON | -    | 14   | 17   | mA   |

| Zener Voltage            | Vz       | ICC = 25mA     | 30   | 38   | -    | V    |

Adjust VCC above the start threshould before setting at 15V

#### Note:

- 1. Parameter measured at trip point of latch

- 2. Gain defined as:

$$A = \frac{\Delta V_{pin1}}{\Delta V_{pin3}} \quad , 0 \le V pin3 \le 0.8 V$$

3. These parameters, although guaranteed, are not 100 tested in production.

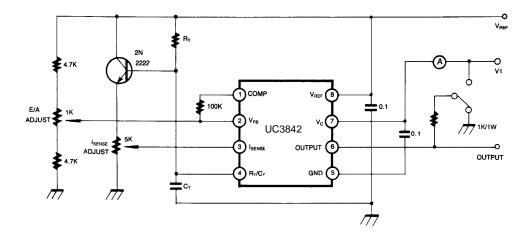

Figure 1. Open Loop Test Circuit

High peak currents associated with capacitive loads necessitate careful grounding techniques Timing and bypass capacitors should be connected close to pin 5 in a single point ground. The transistor and  $5k\Omega$  potentiometer are used to sample the oscillator waveform and apply an adjustable ramp to pin 3.

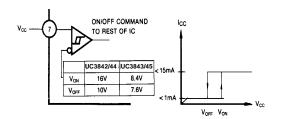

Figure 2. Under Voltage Lockout

During Under-Voltage Lock-Out, the output driver is biased to a high impedance state. Pin 6 should be shunted to ground with a bleeder resistor to prevent activating the power switch with output leakage current.

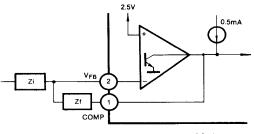

Error amp can source or sink up to 0.5mA

Figure 3. Error Amp Configuration

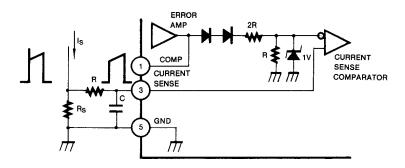

Figure 4. Current Sense Circuit

Peak current (Is) is determined by the formula:

$$I_{S}(MAX) = \frac{1.0V}{R_{S}}$$

A small RC filter may be required to suppress switch transients.

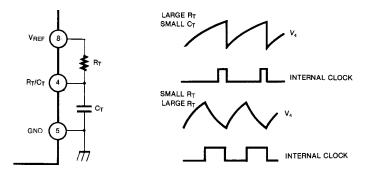

Figure 5. Oscillator Waveforms and Maximum Duty Cycle

Oscillator timing capacitor, C<sub>T</sub>, is charged by V<sub>REF</sub> through R<sub>T</sub> and discharged by an internal current source. During the discharge time, the internal clock signal blanks the output to the low state. Selection of R<sub>T</sub> and C<sub>T</sub> therefore determines both oscillator frequency and maximum duty cycle. Charge and discharge times are determined by the formulas: t<sub>c</sub> = 0.55 R<sub>T</sub> C<sub>T</sub>

$$t_{D} = R_{T}C_{T}I_{n}\left(\frac{0.0063R_{T}-2.7}{0.0063R_{T}-4}\right)$$

Frequency, then, is:  $f=(t_c + t_d)^{-1}$

For RT > 5K

$$\Omega$$

, f =  $\frac{1.8}{R_T C_T}$

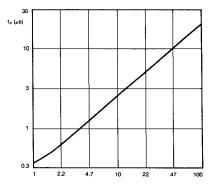

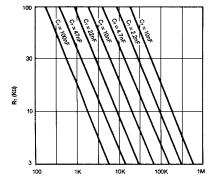

Figure 6. Oscillator Dead Time & Frequency

Figure 7. Timing Resistance vs Frequency

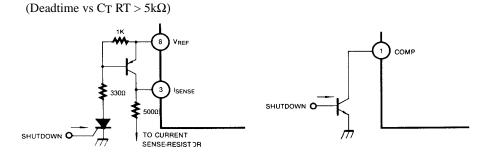

Figure 8. Shutdown Techniques

Shutdown of the UC3842 can be accomplished by two methods; either raise pin 3 above 1V or pull pin 1 below a voltage two diode drops above ground. Either method causes the output of the PWM comparator to be high (refer to block diagram). The PWM latch is reset dominant so that the output will remain low until the next clock cycle after the shutdown condition at pins 1 and/or 3 is removed. In one example, an externally latched shutdown may be accomplished by adding an SCR which will be reset by cycling V<sub>CC</sub> below the lower UVLO threshold. At this point the reference turns off, allowing the SCR to reset.

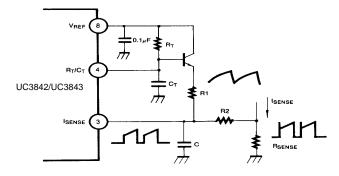

#### Figure 9. Slope Compensation

A fraction of the oscillator ramp can be resistively summed with the current sense signal to provide slope compensation for converters requiring duty cycles over 50%. Note that capacitor, C<sub>T</sub>, forms a filter with R2 to suppress the leading edge switch spikes.

Figure 11. Temperature Drift (Ist)

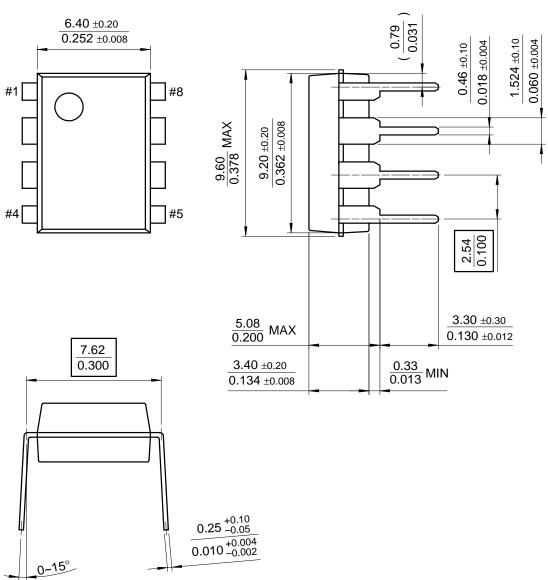

# **Mechanical Dimensions**

# Package

8-DIP

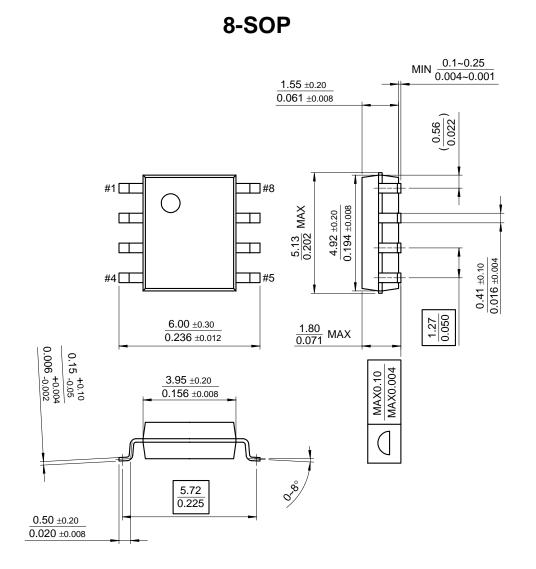

# Mechanical Dimensions (Continued)

### Package

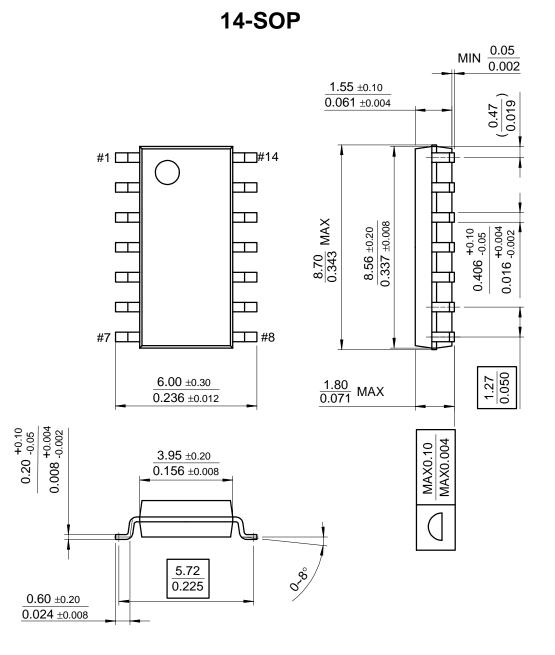

## Mechanical Dimensions (Continued)

### Package

# **Ordering Information**

| Product Number | Package | Operating Temperature |

|----------------|---------|-----------------------|

| UC3842N        |         |                       |

| UC3843N        | 8-DIP   |                       |

| UC3844N        | 0-DIP   |                       |

| UC3845N        |         |                       |

| UC3842D1       | 8-SOP   |                       |

| UC3843D1       |         | 0 ~ + 70°C            |

| UC3844D1       |         | 0~+70 C               |

| UC3845D1       |         |                       |

| UC3842D        | 14-SOP  |                       |

| UC3843D        |         |                       |

| UC3844D        |         |                       |

| UC3845D        |         |                       |

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Fairchild Semiconductor:UC3843D1UC3843DXUC3843DUC3843D1UC3843DXUC3843D