Data sheet acquired from Harris Semiconductor SCHS063

# CD4094B Types

# **CMOS** 8-Stage Shift-and-Store **Bus Register**

High-Voltage Types (20-Volt Rating)

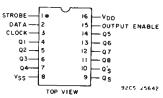

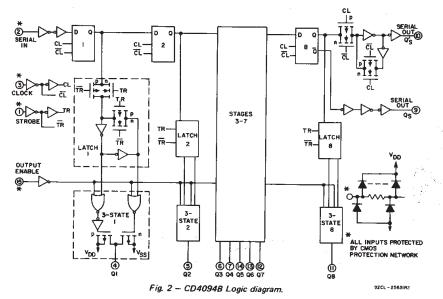

■ CD4094B is an 8-stage serial shift register having a storage latch associated with each stage for strobing data from the serial input to parallel buffered 3-state outputs. The parallel outputs may be connected directly to common bus lines. Data is shifted on positive clock transitions. The data in each shift register stage is transferred to the storage register when the STROBE input is high. Data in the storage register appears at the outputs whenever the OUTPUT-ENABLE signal is high.

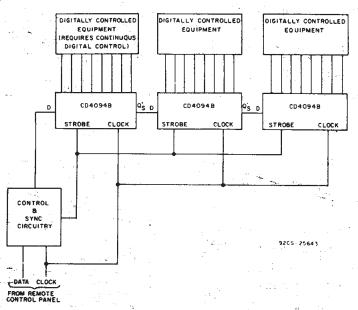

Two serial outputs are available for cascading a number of CD4094B devices. Data is available at the OS serial output terminal on positive clock edges to allow for high-speed operation in cascaded systems in which the clock rise time is fast. The same serial information, available at the  $Q_S^\prime$  terminal on the next negative clock edge, provides a means for cascading CD4094B devices when the clock rise time is slow.

The CD4094B types are supplied in 16-lead hermetic dual-in-line ceramic packages (D and F suffixes), 16-lead dual-in-line plastic package (E suffix), and in chip form (H suffix).

# Features:

- 3-state parallel outputs for connection to common bus

- Separate serial outputs synchronous to both positive and negative clock edges for cascading

- Medium speed operation -- 5 MHz at 10 V (typ.)

- Standardized, symmetrical output characteristics

- 100% tested for quiescent current at 20 V

- Maximum input current of 1 µA at 18 V over full package temperature range; 100 nA at 18 V and 25°C

- Noise margin (full package temperature range): 1 V at V<sub>DD</sub> = 5 V 2 V 2 V 2.5 V at V<sub>DD</sub> = 15 V 2 V at V<sub>DD</sub> = 10 V

- 5-V, 10-V, and 15-V parametric ratings

- Meets all requirements of JEDEC Tentative Standard No. 13B, "Standard Specifications for Description of 'B' Series CMOS Devices'

# Applications:

- Serial-to-parallel data conversion

- Remote control holding register

- Dual-rank shift, hold, and bus applications

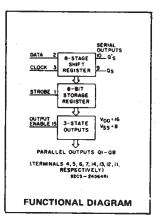

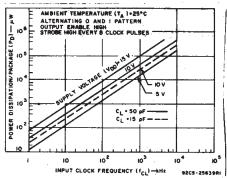

Fig. 1 - Terminal assignment,

### MAXIMUM RATINGS, Absolute-Maximum Values: DC SUPPLY-VOLTAGE RANGE, (VDD)

| VSS Terminal)0.5V                            | to +20V |

|----------------------------------------------|---------|

| E, ALL INPUTS0.5V to V                       | n +0.5V |

| NY ONE INPUT                                 | .+10mA  |

| PER PACKAGE (PD):                            |         |

| 00°C                                         | 500mW   |

| 125°C Derate Linearity at 12mW/°C to         | 200mW   |

| PER OUTPUT TRANSISTOR                        |         |

| AGE-TEMPERATURE RANGE (All Package Types)    | 100mW   |

| TURE RANGE (TA)55°C to                       | +125°C  |

| RE RANGE (Tstg)65°C to                       | +150°C  |

| DURING SOLDERING):                           |         |

| 2 inch (1.59 ± 0.79mm) from case for 10s max | +265°C  |

|                                              |         |

Fig. 3 - Timing diagram.

9205 25632

# CD4094B Types

**RECOMMENDED OPERATING CONDITIONS** at  $T_A = 25^{\circ}C$ , Except as Noted. For maximum reliability, nominal operating conditions should be selected so that operation is always within the following ranges:

| CHARACTERISTIC                                               | VDD      | LIN  |        |         |  |

|--------------------------------------------------------------|----------|------|--------|---------|--|

| CHARACTERISTIC                                               | (V)      | MIN. | MAX.   | UNITS   |  |

| Supply-Voltage Range (For TA=Full Package-Temperature Range) |          | 3    | 18     | V       |  |

|                                                              | 5        | 125  | 1 _    |         |  |

| Data Setup Time, ts                                          | 10       | 55   |        | ns      |  |

|                                                              | 15       | 35   | -      | 1       |  |

|                                                              | 5        | 200  | _      |         |  |

| Clock Pulse Width, tw                                        | 10       | 100  | -      | ns      |  |

|                                                              | 15       | 83   |        |         |  |

|                                                              | 5        |      | 1.25   |         |  |

| Clock Input Frequency, fcL                                   | 10       | dc   | 2.5    | MHz     |  |

|                                                              | 15       |      | 3      |         |  |

| -Clock Input Rise or Fall time,                              | 5        |      | 15     | <b></b> |  |

| t <sub>r</sub> CL, t <sub>f</sub> CL:*                       | 10<br>15 |      | 5<br>5 | μs      |  |

|                                                              | 5        | 200  | -      |         |  |

| Strobe Pulse Width, tw                                       | 10       | 80   | -      | ns      |  |

|                                                              | 15       | 70   | - 1    |         |  |

<sup>\*</sup>If more than one unit is cascaded trCL (for Qs only) should be made less than or equal to the sum of the fixed propagation delay at 50 pF and the transition time of the output driving stage for the estimated capacitive load.

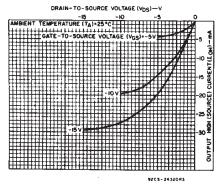

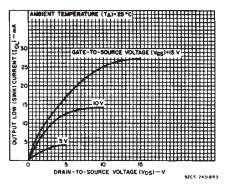

Fig. 5 — Minimum output low (sink) current characteristics.

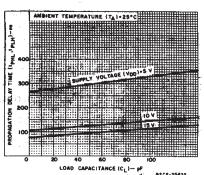

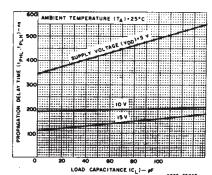

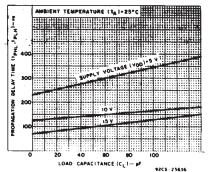

Fig. 8 — Clock-to-serial output  $Q_S$  propagation delay vs  $C_L$ .

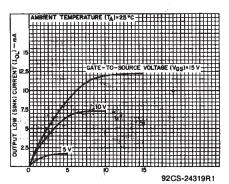

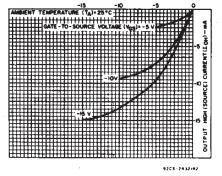

Fig. 6 — Typical output high (source) current characteristics.

Fig. 9 — Clock-to-serial output Q'S propagation delay vs C<sub>L</sub>.

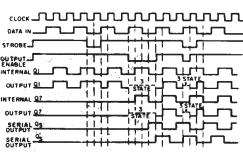

TRUTH TABLE

| CL <sup>A</sup> Output<br>Enable | Strobe | Data |    | railei<br>tputs | Serial<br>Outputs |            |    |

|----------------------------------|--------|------|----|-----------------|-------------------|------------|----|

|                                  | 311000 | Date | Q1 | QN              | os.               | 0.2        |    |

|                                  | 0      | х    | Х  | ОС              | ос                | Q7         | NC |

| $  \setminus  $                  | 0      | ×    | х  | ос              | oc                | NC         | Q7 |

| \                                | - 1    | ٥    | х  | NC:             | NC                | Q7         | NC |

| 1                                | 111    | 1 1  | Ö  | 0               | QN-1              | <b>Q</b> 7 | NC |

| \ <u>_</u>                       | 1 -    | 1    | 1  | 1               | QN-1              | Q7         | NC |

| 1                                | 1      | 1    | 1  | NC              | NC                | NC         | Q7 |

- \* = Level Change X = Don't Care NC = No Change

- Logic 1 ≡ High Logic 0 ≡ Low

- NC = No Change OC = Open Circuit

- At the positive clock edge information in the 7th shift register stage is transferred to the 8th register stage and the OS output.

Fig. 4 — Typical output low (sink) current characteristics.

#### DRAIN-TO-SOURCE VOLTAGE (VDS)-1

Fig. 7 — Minimum output high (source) current characteristics.

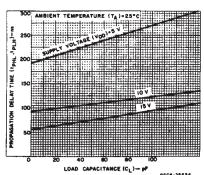

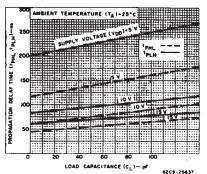

Fig. 10 — Clock-to-parallel output propagation delay vs  $C_L$ .

# CD4094B Types

# STATIC ELECTRICAL CHARACTERISTICS

| CHARACTER-                                     | CONDITIONS     |      |     | LIMITS AT INDICATED TEMPERATURES (°C) |       |       |       |       |                   | UNITS |        |

|------------------------------------------------|----------------|------|-----|---------------------------------------|-------|-------|-------|-------|-------------------|-------|--------|

| ISTIC                                          | ٧o             | VIN  | VDD |                                       |       |       |       |       | +25               |       | ONT    |

| ,                                              | . (V)          | (V)  | (V) | -55                                   | -40   | +85   | +125  | Min.  | Тур.              | Max.  |        |

| Quiescent Device                               | -              | 0,5  | 5   | 5                                     | 5     | 150   | 150   | _     | 0.04              | 5     |        |

| Current,<br>IDD Max.                           | _              | 0,10 | 10  | 10                                    | 10    | 300   | 300   | _     | 0.04              | -10   | μΑ     |

|                                                |                | 0,15 | 15  | 20                                    | 20    | 600   | 600   | - ,   | 0.04              | 20    | 1 44   |

|                                                | _              | 0,20 | 20  | 100                                   | 100   | 3000  | 3000  | - ;   | 0.08              | 100   | :      |

| Output Low                                     | 0.4            | 0,5  | 5   | 0.64                                  | 0.61  | 0.42  | 0.36  | 0.51  | 1                 | -     |        |

| (Sink) Current                                 | 0.5            | 0,10 | 10  | 1.6                                   | 1.5   | 1.1   | 0.9   | 1.3   | 2.6               | -     |        |

| IOL Min.                                       | 1.5            | 0,15 | 15  | 4.2                                   | 4     | 2.8   | 2.4   | 3 4   | 6.8               | 12.   |        |

| Output High                                    | 4.6            | 0,5  | 5   | -0.64                                 | -0.61 | -0.42 | -0.36 | -0.51 | -1                | -     | mA     |

| (Source)                                       | 2.5            | 0,5  | 5   | -2                                    | -1.8  | -1.3  | -1.15 | -1.6  | -3.2              | ,     |        |

| Current,<br>IOH Min.                           | 9.5            | 0,10 | 1.0 | -1.6                                  | -1.5  | -1.1  | -0.9  | -1.3  | -2.6              |       |        |

| 10H WIII.                                      | 13.5           | 0,15 | 15  | -4.2                                  | -4    | -2.8  | -2.4  | -3.4  | -6.8              |       |        |

| Output Voltage:                                | -              | 0,5  | 5   |                                       | 0     | .05   |       | -     | 0                 | 0.05  |        |

| Low Level,<br>VOL Max.                         | -              | 0,10 | 10  | 0.05                                  |       |       |       | - ,   | 0                 | 0.05  | ·<br>v |

| VOL Wax.                                       |                | 0,15 | 15  | 0.05                                  |       |       |       | - :   | 0                 | 0.05  |        |

| Output Voltage:                                | -              | 0,5  | 5   | 4.95 4.95 5 -                         |       |       |       |       | -                 | ,     |        |

| High Level,                                    | -              | 0,10 | .10 | 9.95                                  |       |       |       | 9.95  | 10                | -     |        |

| VOH Min.                                       |                | 0,15 | 15  | 14.95                                 |       |       |       | 14.95 | 15                | -     |        |

| Input Low                                      | 0.5, 4.5       | -    | 5   | 1,5                                   |       |       |       | _     |                   | 1.5   |        |

| Voltage,                                       | 1, 9           | -    | 10  |                                       |       | 3     |       | _     | _                 | 3     |        |

| VIL Max.                                       | 1.5,13.5       | -    | 15  | 4                                     |       |       |       |       |                   | 4     |        |

| Input High                                     | 0.5, 4.5       | -    | 5   |                                       | 3     | 3.5   |       | 3.5   | -                 | _     | V      |

| Voltage,                                       | 1, 9           |      | 10  | 7                                     |       |       |       | 7     |                   |       |        |

| VIH Min.                                       | 1.5,13.5       | -    | 15  |                                       | 1     | 1     |       | 11    | [                 | _ `   |        |

| Input Current<br>IJN Max.                      | <del>-</del> . | 0,18 | 18  | ±0.1                                  | ±0.1  | ±1    | ±1    | -     | ±10 <sup>-5</sup> | ±0.1  | μΑ     |

| 3 State Output<br>Leakage Current<br>IOUT Max. | 0,18           | 0,18 | 18  | ±0.4                                  | ±0.4  | ±12   | ±12   |       | ±10~4             | ±0.4  | μΑ     |

Fig. 14 - Remote control holding register.

Fig. 11 – Strobe-to-parallel output propagation delay vs C<sub>L</sub>.

Fig. 12 — Output enable-to-parallel output propagation delay vs  $C_L$ .

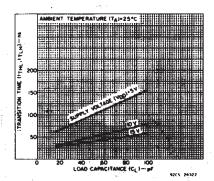

Fig. 13 - Typical transition time vs. load capacitance.

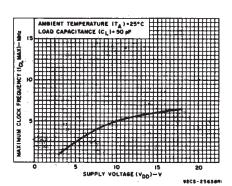

Fig. 15 — Typical maximum-clock-frequency vs. supply voltage.

#### **DYNAMIC ELECTRICAL CHARACTERISTICS**

At  $T_A=25^{\circ}C$ ; Input  $t_f$ ,  $t_f=20$  ns,  $C_L=50$  pF,  $R_L=200$  k $\Omega$

| CHARACTERISTIC                                     | V <sub>DD</sub> |          | UNITS      |            |          |  |

|----------------------------------------------------|-----------------|----------|------------|------------|----------|--|

|                                                    | (V)             | MIN.     | TYP.       | MAX.       | UNITS    |  |

| Propagation Delay Time,                            |                 |          |            |            |          |  |

| tPHL, tPLH                                         | 5               |          | 200        | 000        |          |  |

| Clock to Serial Output Q <sub>S</sub>              | 10              | _        | 300<br>125 | 600<br>250 |          |  |

| Clock to Serial Output US                          | 15              |          | 95         | 190        | ns       |  |

|                                                    | 5               | _        | 230        | 460        |          |  |

| Clock to Serial Output Q'S                         | 10              | _        | 110        | 220        | l ns     |  |

| 55.00                                              | 15              | _        | 75         | 150        | "        |  |

|                                                    | 5               |          | 420        | 840        |          |  |

| Clock to Parallel Output                           | 10              | _        | 195        | 390        | ns       |  |

|                                                    | 15              | -        | 135        | 270        |          |  |

|                                                    | - 5             | <u> </u> | 290        | 580        |          |  |

| Strobe to Parallel Output                          | 10              | -        | 145        | 290        | ns       |  |

|                                                    | 15              |          | 100        | 200        | <u> </u> |  |

| Output Enable to Parallel                          | 5               | _        | 140        | 280        |          |  |

| Output:                                            | 10              | -        | 60         | 120        | ns       |  |

| t <sub>PHZ</sub> , t <sub>PZH</sub>                | 15              | _        | 45         | 90 `       |          |  |

|                                                    | 5               | _        | 100        | 200        |          |  |

| tPLZ, tPZL                                         | 10              | -        | 50         | 100        | ns       |  |

|                                                    | 15              | -        | 40         | 80         | <u></u>  |  |

| Minimum Strobe Pulse                               | 5               | _        | 100        | 200        |          |  |

| Width, tw                                          | 10              | -        | . 40       | 80         | ns       |  |

|                                                    | 15              |          | 35         | 70         |          |  |

| Minimum Clock Pulse                                | 5               | -        | 100        | 200        |          |  |

| Width, tw                                          | 10              | _        | 50         | 100        | ns       |  |

|                                                    | 15              |          | 40         | 83         |          |  |

| Minimum Data Setup                                 | 5               | -        | 60         | 125        |          |  |

| Time, t <sub>S</sub>                               | 10              | _        | 30         | 55         | ns       |  |

| · · · ·                                            | 15              |          | 20         | 35         |          |  |

| Transition Time;                                   | 5               | -        | 100        | 200        |          |  |

| THL, TLH                                           | 10              |          | 50         | 100        | ns       |  |

| COMPANIE CONTRACTOR                                | 15              | _        | 40         | 80         |          |  |

| Maximum Clock Input Rise                           | 5<br>10         | 15<br>5  |            | -          | 146      |  |

| or Fall Time, t <sub>r</sub> CL, t <sub>f</sub> CL | 15              | 5        |            | _          | μs       |  |

| Maximum Clock Input                                | 5               | 1.25     | 2.5        |            |          |  |

| Frequency, fcL                                     | 10              | 2.5      | . 5        | -          | MHz      |  |

| <u> </u>                                           | 15              | 3        | 6          |            |          |  |

| Input Capacitance CIN                              |                 |          | 5          | 7.5        | pF       |  |

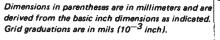

Fig. 16 – Dynamic power dissipation vs input clock frequency.

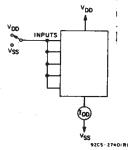

Fig. 17 — Quiescent device current test circuit.

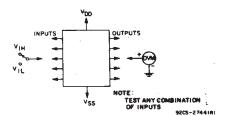

Fig. 18 - Input voltage test circuit.

Fig. 19 - Input current test circuit.

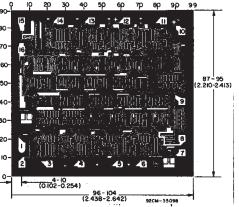

Dimensions and Pad Layout for CD4094B Chip.